Member-only story

Compressed 16-bit RISC-V instructions compared to AVR

Since AVR uses mostly 16-bit instructions it would be interesting to compare with 16-b RISC-V instructions

RISC-V has compressed instructions extension C, which with a mere 400 gates added gives a RISC-V processor 16-bit instructions. I thought it would be interesting to compare these 27 instructions with instructions from the AVR microprocessor, a well-known processor for microcontrollers (used in Arduino). This will compare with a subset of the 78 instructions which exist for AVR.

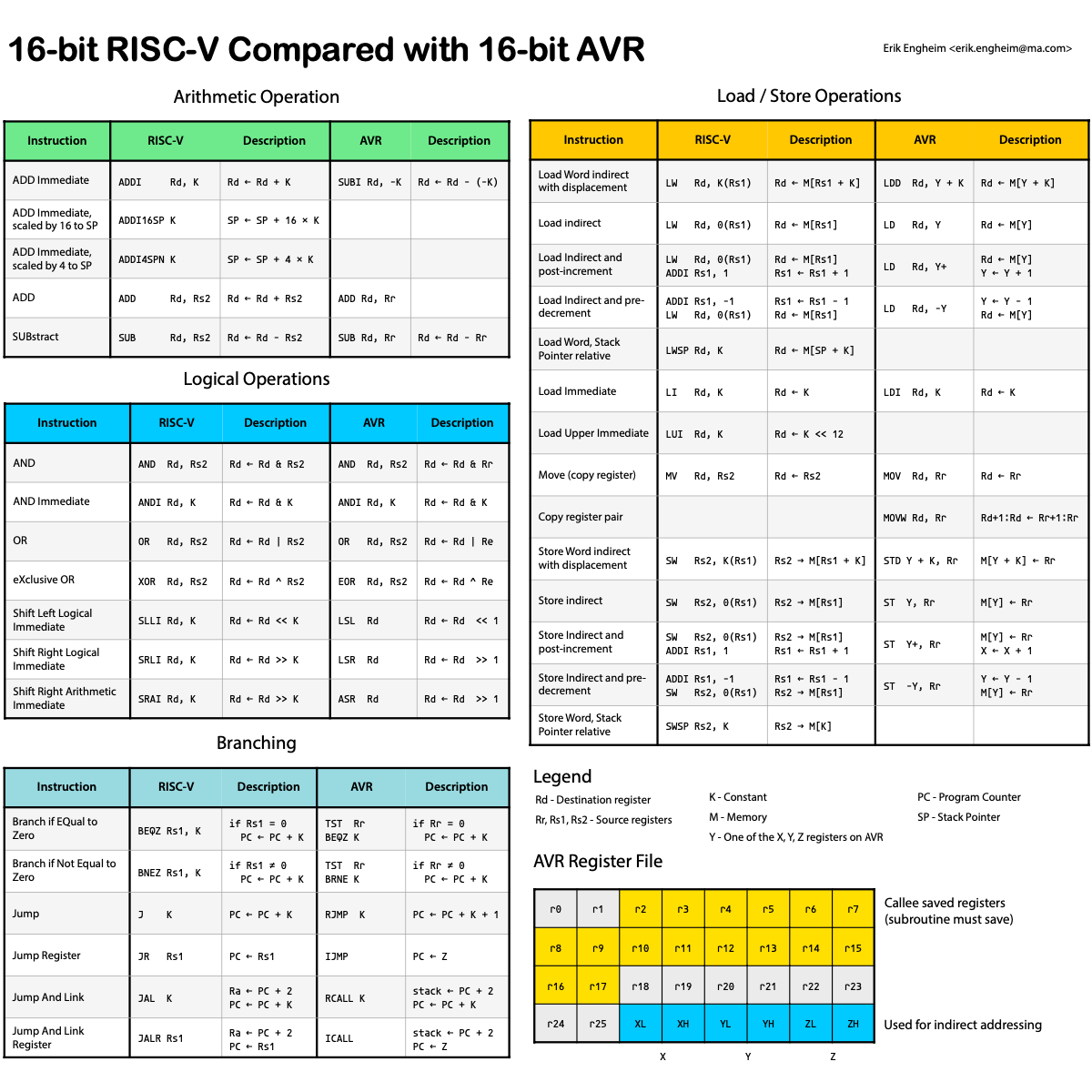

The “cheatsheet” below has been made by finding some compromises between what is common RISC-V and AVR notation to describe assembly instructions. I have used the AVR convention of using K to describe immediate values. Registers are capitalized like Rd, Rr, Rs1 and Rs2 in line with AVR conventions. When accessing value at memory location K, AVR would have written (K) but I have decided to use a more RISC-V-like approach of writing M[K]. In cases where there is no good mapping between instructions I have either skipped writing a comparable instruction or written combination of instructions.

PDF for better readability: RISC-V and AVR instruction-sets compared.

When you only got 16-bits to play with to encode instructions, then you have to make numerous compromises. I think it is interesting to compare some of the compromises made by both architectures.

RISC-V Restrictions on Register Use

To support 32 registers, you need to set aside 5 bits to encode a register. If your instruction does a lot of things such adding a constant or jumping to a particular address with an offset, then you are not left with a lot of bits to play with. For this reason, both AVR and RISC-V when using 16-bit instructions don’t allow you to address all registers.

RV32C (compressed instructions for RISC-V) only allow you to specify directly the 8 most commonly used registers s0, s1, a0 to a5. That is because only 3 bits are set aside to specify registers. There are some exceptions. The MV (MoVe), ADD, ADDI (ADD Immediate), LWSP (Load Word from SP) and SWSP (Store Word from SP) give access to all 32 RISC-V registers.