Member-only story

Very Long Instruction Word Microprocessors

RISC and CISC type microprocessors are not the only game in town. VLIW microprocessors where once believed to be the future but not anymore. What happened?

In the early 2000s Very Long Instruction Word (VLIW) microprocessors was all the hype to the point of causing several chip makers to simply drop developing their chip development process and sit back waiting for microprocessor Nirvana to arrive.

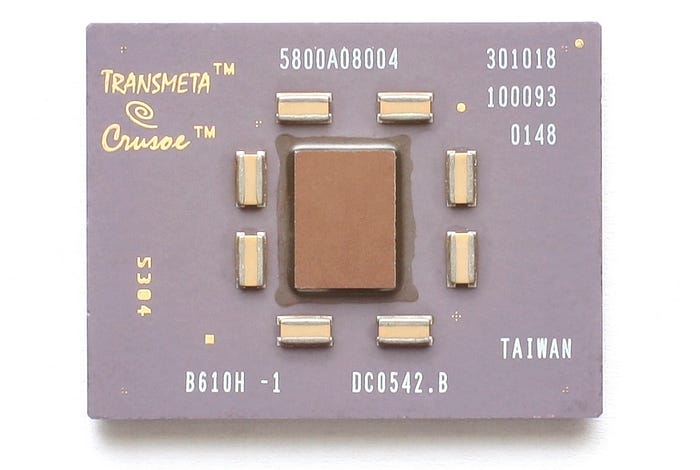

Transmeta with their Crusoe and Intel with their Itanium processors promised to bring about this VLIW revolution. Except if you look around, we are not in fact living in a a VLIW microprocessor Utopia.

So let us look at what these VLIW processors are like and try to explain why they failed.

Doing Work in Parallel

Because we cannot increase the clock frequency of microprocessor much anymore without overheating them, everything is really centered around way of doing as much work as possible in parallel.

We have developed a number of ways of doing this. The most straightforward approach is to have multiple microprocessor cores. Each core basically runs a separate program. This could be actual separate programs or programmers can split up their own programs in a such a way that parts of the program runs as if program was made up of smaller programs. We call these tasks, and each task can run on a separate microprocessor core.

Another popular approach is to not perform multiple instructions in parallel but instead have instructions with manipulate multiple numbers at the same time. We typically call this vector processing. Computer graphics often lend itself to that sort of processing.

Read more: RISC-V Vector Instructions vs ARM and x86 SIMD

Scalar vs Superscalar Processors

A CPU core which performs one instruction at a time is called a scalar processor. So a CPU with multiple cores is still a scalar CPU because the individual cores are scalar. However if one core is able to execute multiple instructions each clock cycle we call it superscalar. VLIW microprocessors are a type of superscalar…